|

以下文章来源于半导体产业洞察 ,编辑IAN CUTRESS

据先容,台积电每年生产相当于 110到120万片的12 英寸晶圆。目前其收入的 50% 或更高(23Q2 为 53%)来自两种领先的节点技术:7nm 和 5nm,3nm 的收入将在今年年底实现,这些节点约占晶圆的 20%体积。如果按应用平台划分,大约 44% 的收入来自 HPC,33% 来自智能手机,其余部分则分布在物联网、汽车和其他领域。

就台积电的生产布局而言,它在台湾拥有四家超级工厂,专注于 12 英寸生产。这些巨型晶圆厂是分阶段建设的,其中台积电自 2020 年以来将建设新阶段的速度从每年 2 个提高到每年 5 个。与这些巨型晶圆厂一起建设的还有 APF6,即先进封装 Fab 6,于2023年 6 月开业。

至于备受关注的台积电 N3,则来自台南 Fab 18 的第 5、6 和 8 期,而台积电未来的 N2 将进入新晶圆厂——新竹的 Fab 20 和台中的新厂址台。台积电近两年已开工10期,其中5期是在台湾的制造、2期是在台湾的先进封装、3期在海外。

台积电的海外业务包括自 2018 年开业的中国南京一座晶圆厂(Fab 16)、日本熊本的一座新晶圆厂(Fab 23)以及亚利桑那州的两座新晶圆厂(Fab 21)。亚利桑那州的第一个工厂已开始接收设备,以期在 2024 年实现 N4 的批量生产。亚利桑那州的第二个工厂正在建设中,为 N3 建造。亚利桑那州的目标是每年生产 60 万片晶圆,或者每月启动 5 万片晶圆。根据一贯的做法,一座 Gigafab 每月产量超过 10 万片,所以亚利桑那州现在只是 Gigafab 的一半。

在日本,熊本工厂已开始生产目前需求量很大的 16/12 纳米和 28 纳米特种技术,预计于 2024 年实现量产。台积电还表示,中国新扩建的工厂于 2022 年开始量产 28 纳米技术。此外,作为制程的一部分,台积电已经将机器学习集成到其生产流程中,以保持质量和一致性,同时也优化客户的产量和生产。

台积电 N3、N3E、N3P、N3X

有很多报道称,由于台积电决定在 N3 中坚持使用 FinFET 技术,因此报道称台积电无法获得性能优势,并且存在一些延迟。以下是台积电向大家先容的有关其技术的内容。

首先,在良率方面,当前的 N3 具有与 N5 在当前开发和生产阶段相同的缺陷密度 (D0:defect density),台积电表示他们在大批量生产中具有“行业领先”的良率。他们预计 N3 缺陷率将按预期追随 N5,并在适当的时候达到同等水平。请注意,N5 缺陷率约为每平方厘米 0.07 个(或每个晶圆 40-45 个)

这里有很多数字需要出合理,但我会和你一起回顾一下。所有这些数字均引用了 Arm Cortex-A715 内核示例,这是最新的内核设计之一。

TSMC 表示,从 N5 到 N3E,N3E 的速度(频率)提高了 18%,密度提高了 30-60%(具体取决于 SoC 与逻辑),并且功耗降低了 32%;N4PRF 则是 N4 的射频优化版本,预计将于 2023 年下半年/2024 年初进行风险生产。

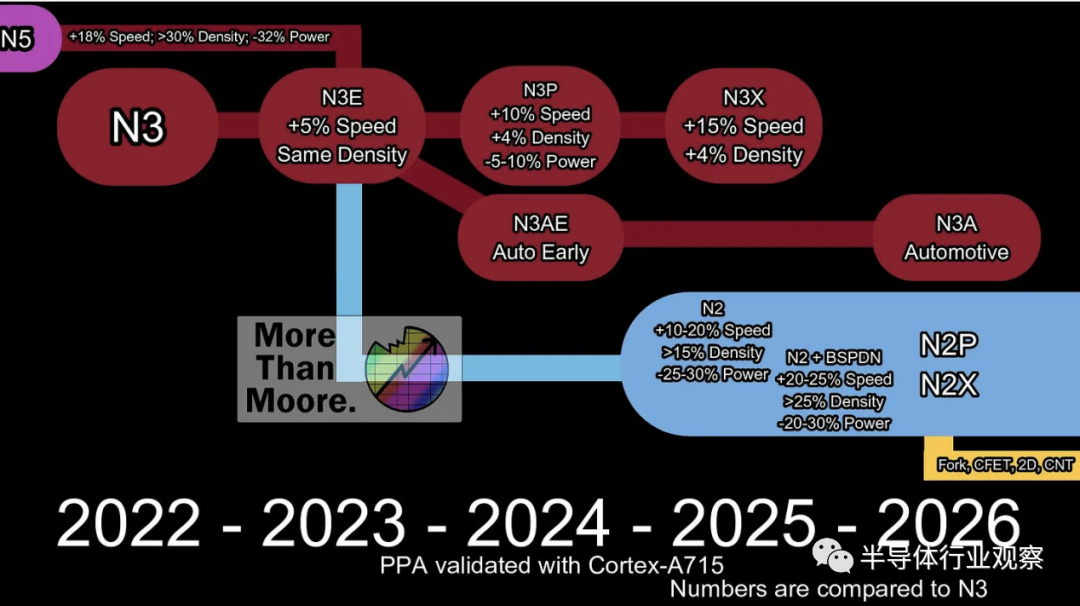

来到3nm节点,N3 将于 2022 年第四季度进入量产;N3E 同样将于 2023 年第四季度进入量产,速度提高 5%,密度不变。N3E 已通过性能和良率目标;N3P 将跟随 N3E,于 2024 年 2H 投入生产。与 N3(非 N3E)相比,N3P 与 N3(非 N3E)相比频率增加 10%,密度增加 4%;N3X 是更高性能的版本,将于 2025 年量产。与标准 N3 相比,它在相同功率下提供 +15% 的速度和 +4% 的密度。

就目前情况而言,N3E 的几乎所有 IP 均已准备就绪并经过硅验证,其中 UCIe 和 HBM3 是最后完成的两个主要部分(但今天已获得硅前支撑)。相比之下,N3P IP 大多仍处于投片前支撑或仍在开发/规划中。

台积电还将开发 N3 的汽车级版本,这基本会发生在主工艺出货100 万片晶圆后,台积电才后再创建汽车级版本,这会造成 2-3 年的滞后,但在这种情况下,需求足够高。此外,台积电将创建N3AE,帮助客户比平常更早地进行设计。N3A(完整版本)将于 2026 年推出。台积电表示,他们认为 N3AE 更多的是消费级版本,而 N3A 将是适合企业部署的完整版本。

台积电 N2、N2X、N2P、BSPDN

现在大家转向台积电的 N2 路线图,即使用环栅晶体管的工艺节点。

TSMC 使用 Cortex A715 作为基础设计,声称 N3E 节点速度提高了 5-15%,密度提高了 15% 以上,功耗降低了约 25-30%。图中的数字将其转换为与基本 N3 的比较,只是为了保持一致性,但这些数字可能是非此即彼,而不是组合。

据消息人士透露,制造这些新晶体管的困难部分实际上是晶体管本身的一致性,因此台积电似乎需要时间来解决它。TSMC 表示,N2 功耗降低的很大一部分是其设计提供的最低电压较低,这应该可以满足当前对高效硬件的需求。N2 的时间表涉及 2025 年的风险生产,那就意味着到下半年,芯片产能增加。

在 N2 的 EDA 方面,台积电表示所有主要 EDA 工具和供应商均已通过认证。这包括来自 Synopsys 的完整 EDA 堆栈(包括与 Ansys 合作开发 EMIR)、来自 Cadence 的几乎完整堆栈(具有 EMIR,而不是 Tx STA)以及来自 Synopsys、Cadence 和西门子EDA的模拟器(Simulator)。

来到性能数据方面(据说与 A715 进行比较)。

对于 N3,台积电推出了一种名为 FinFlex 的新设计模型,允许晶体管使用不同数量的栅极来实现高性能(称为 3-2)或高密度(2-1)设计。高性能设计允许更高的频率,但会降低功耗,而高密度则允许更紧凑的设计,但不能推动太多。

之所以会有这个想法,是因为现代 HPC 核心(例如 x86 或 Arm 核心)将使用性能晶体管,而 IO 和效率核心可能会使用密集晶体管。N2 似乎还没有 FinFlex 产品,但将两种晶体管类型与标准 N2 产品进行比较时,N2 在等频率下的功耗减少了 30%,在等功率下的频率减少了 13%。这与他们报告的数字相符,但台积电为这些数字提供了更多选择。

值得注意的是,台积电的常规 N2 工艺节点不会采用称为背面供电(BSPDN)的技术。这项技术改变了芯片的构建方式——不是将晶体管上方的电源连接和信号连接交织在一起,而是将两种类型的连接分开——电源在背面,信号在正面。

因为BSPDN是一项复杂的技术,所以TSMC 将在周期后期提供带有 BSPDN 的 N2 版本——与标准 N2 相比大约晚六个月。BSPDN 的优点还包括更简单的设计规则,但增加了密度(比常规 N2 增加10%)和速度(增加5%到10%)。功耗似乎有点难以判断,因为更高效率的权衡之一是更低的功耗或更高的性能,而且台积电似乎专注于 BSPDN 的性能方面,特别是由于功率信号/数据信号串扰较少。

同时,大家还发现了与 TSMC Wafer-on-Wafer 技术类似的东西——Graphcore 在 N7 上使用 WoW 将一些 MIM 电容器从金属堆栈的上层迁移到单独的芯片中,从而使它们更大并且更不易受到干扰,这带来的最终结果是更高的效率据报道,这种技术可以提高频率,使性能提高 30%。

BSPDN 更复杂,因为它将所有功能都放在了背面,但没有像WoW那样带来重大变化,因此带来的好处可能会受到削弱。与其他节点相比,N2 + BSPDN 似乎还没有被赋予特定的名称,因此大家将看看随着时间的推移它是否会发生变化。

TSMC 同时还提供 N2 和 N2+BSPDN 作为不同的变体将成为行业规范。英特尔已明确表示,对于他们称为 PowerVia 的 BSPDN 版本,这也将是 20A/18A 节点客户的可选附加功能。但由于 BSPDN 涉及的范围更广,似乎两家企业都必须拥有 BSPDN 和非 BSPDN 版本才能满足所有成本模型和设计选择。

在N2 和 N2+BSPDN 之后,台积电已经谈到了 N2P 和 N2X,但提供的细节很少。大家预计这些节点变体将遵循与 N3P 和 N3X 相同的路径(相对于这些节点的速度或密度的微小增加)。

除了 N2 系列之外,TSMC 仍在研究Forksheets(用于密度改进的 GAA 变体)、CFET(也是用于主要密度的 GAA 变体,但可能会牺牲性能) 、2D 晶体管以及碳纳米管等其他潜在技术,但典型的改进可能会在未来十年内出现。

HBM、模拟迁移和3D Fabric

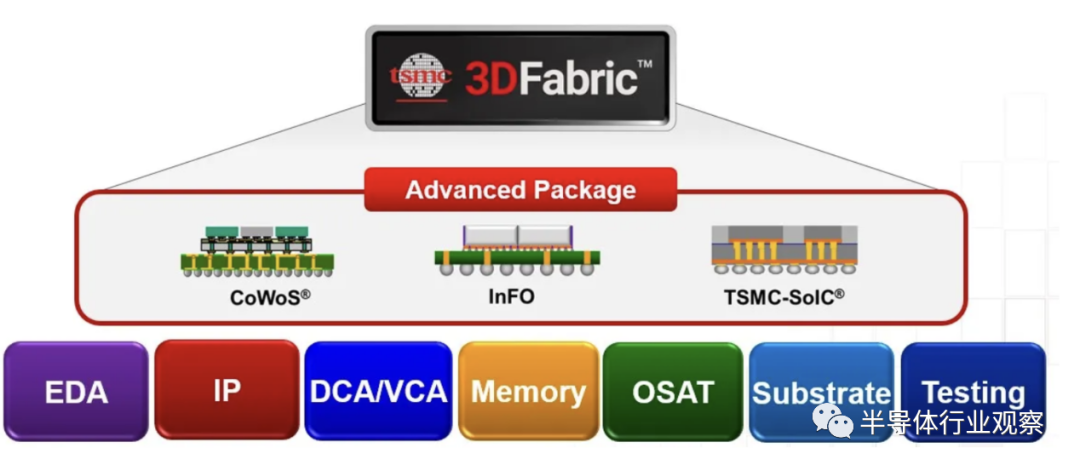

台积电的活动还重点关注了其他技术,例如作为 3DFabric 内存联盟一部分的内存。台积电每月与所有供应商举行小组会议,以确保路线图和封装能力保持一致,并确保 JEDEC 和每个人都保持一致。此次活动的焦点是 HBM3 和 HBM4。以下是台积电对每个合作伙伴的评价。

JEDEC:HBM4 规范与 16Hi 堆栈一致; 美光:宣布推出 9.2 Gbps 的 HBM3 Gen2 产品,并进行 CoWoS 芯片验证; SAMSUNG:HBM3 12Hi 协作可增加 50% 容量,无缓冲(Buffer-less) HBM 研究正在进行中; SK Hynix:HBM3 + HBM4 的CoWoS 协作,HBM4 上的 DTCO,超越 JEDEC 规范,还有 UCIe;

根据此列表,SK Hynix 似乎在 HBM4 方面走得更远,但美光和SAMSUNG都在寻求更高容量或更高带宽的 HBM3。随着对快速、高容量 HBM 的需求不断增加,我相信大多数企业都会采取任何措施 ,但这是可制造性、供应链和一致性的情况。HBM4 使用与 HBM3 相同的频率,但具有双倍引脚以实现双倍带宽,因此它应该是一个“更简单”的迁移。

在制造的模拟方面,台积电也在扩展标准单元的工具包。

TSMC 之前发布了 ADM 1.0,用于模拟设计迁移。在过去,这需要完全定制设计。TSMC 还提供了一种为 N5 和 N3 引入模拟标准单元的方法,现在已扩展到 ADM2.0,提供向后至 N16 并向前至 N2 的标准单元。台积电的目标是继续回到 N28 和 N40,以便获得更广泛的客户采用并缩短上市时间。台积电还着眼于将其引入 N2+BSPDN、Cadence 和 Synopsys 都在原理图迁移、电路优化和布局迁移方面提供全面的 EDA 支撑。

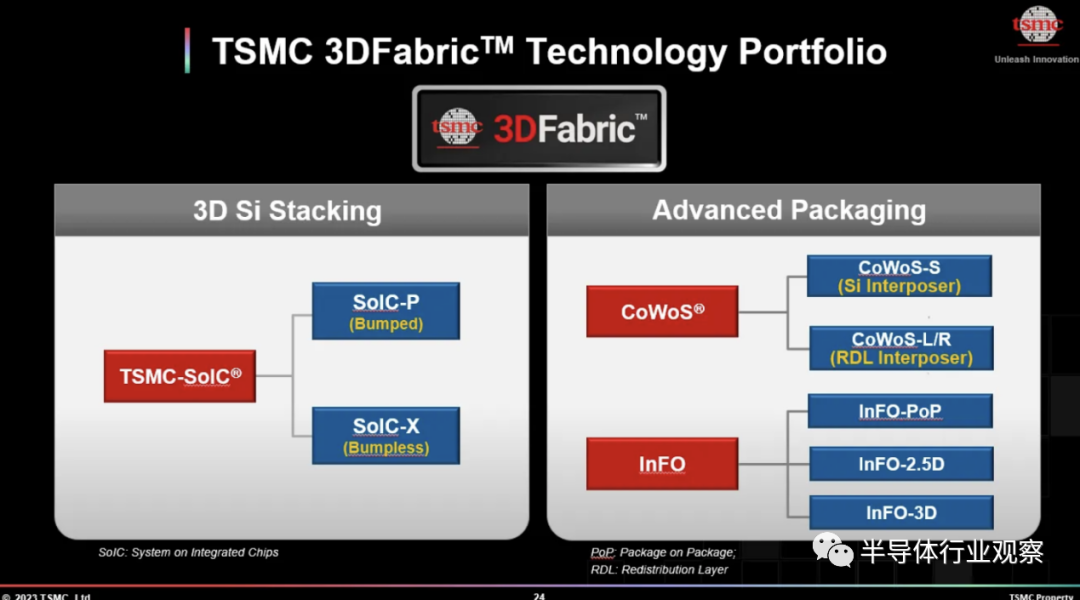

台积电还分享了企业在 3DFabric 联盟以及 3Dblox 封装方面的进展。

根据先容,台积电的目标是为客户提供一组通用的可扩展设计语言,与 EDA 供应商的通用集成工具接口,以便灵活集成下一代昂贵的芯片和这些芯片所需的复杂封装。通过提供 EDA 系统可用于开发和仿真的统一设计语言集,目标是降低芯片上市的端到端成本,并加快上市时间。

3DFabric 作为一个套件提供,包含文档、设计流程和技术文件。其中,一个套件适用于台积电 8 种封装技术。据了解,这些内容分为三类:

Integrated Fan Out (InFO):InFO_oS、InFO_LSI Chip on Wafer on Substrate (CoWoS):CoWoS-S、CoWoS-L、CoWoS-R System on Integrated Circuit (SoIC):SoIC-X、SoIC-P

其中,最前面首先面向市场,而且 InFO 选项也几乎完全来自 3DFabric 套件标准。该套件包含 DRM、DRC、RCX、CAD、PERC、EMIR 等元素,对于 InFO,这两种变体几乎都是完整的。CoWoS-S 也已接近完成,但 L 和 R 仍有一些进展。SoIC-X 大约完成了一半,而 SoIC-P 才刚刚开始。

同时,台积电还对他们与 AMD 在 MI300 上所做的工作非常满意。它使用了多种合作开发的新技术,但台积电还确认 MI300 象限具有基础芯片(quadrants feature base die),其中两个象限(quadrant)是镜像的。每个象限基芯片(quadrant base die)上都有两个图形小芯片或三个 CPU 小芯片,但台积电将其视为 3D 硅集成的前所未有的壮举。

|

265

265

265

265